universal cryptography processor for smart cards eslami et al.: area-efficient universal cryptography processor for smart cards 45 throughput requirements of smart cards and occupies 2.25 mm in 0.18- m 6LM CMOS. A contactless credit card uses RFID technology to enable you to hover or tap a card over a card terminal as a means of conducting a transaction. The card emits short-range electromagnetic waves .

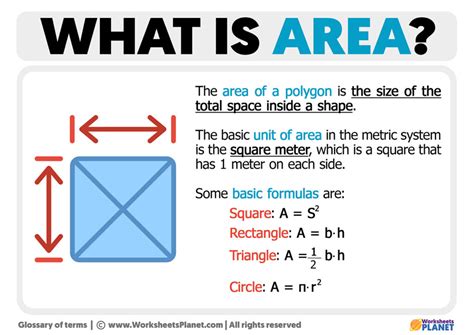

0 · An area

1 · An Area

In Sweden and most of Europe to my knowledge, there’s an rfid chip in all debit and credit cards. You pay by holding your card (or wallet) against the payment terminal. Done. If the total is .

The micro coded cryptography processor is designed for smart card applications, supporting both private key and public key algorithms while meeting the required power and performance standards. Impressively, it is as small as 2.25 mm2 using 0.18-μm 6LM CMOS technology.The microcoded cryptography processor targets smart card applications and implements both private key and public key algorithms and meets the power and performance specifications .

eslami et al.: area-efficient universal cryptography processor for smart cards 45 throughput requirements of smart cards and occupies 2.25 mm in 0.18- m 6LM CMOS.

nintendo nfc reader writer for nintendo 3ds multi ebay iphone

The micro coded cryptography processor is designed for smart card applications, supporting both private key and public key algorithms while meeting the required power and performance standards. Impressively, it is as small as 2.25 mm2 using 0.18-μm 6LM CMOS technology.The microcoded cryptography processor targets smart card applications and implements both private key and public key algorithms and meets the power and performance specifications and is as small as 2.25 mm/sup 2/ in 0.18-/spl mu/m 6LM CMOS.eslami et al.: area-efficient universal cryptography processor for smart cards 45 throughput requirements of smart cards and occupies 2.25 mm in 0.18- m 6LM CMOS. The microcoded cryptography processor targets smart card applications and implements both private key and public key algorithms and meets the power and performance specifications and is as small as 2.25 mm 2 in 0.18-µm 6LM CMOS.

The microcoded cryptography processor targets smart card applications and implements both private key and public key algorithms and meets the power and performance specifications and is as.

An area

This paper proposes a high-performance ASIP (Application specific instruction set processor) for five standard cryptographic algorithms in-cluding both block ciphers (AES, Camellia, and ARIA) and stream ciphers (ZUC and SNOW 3G).The microcoded cryptography processor targets smart card applications and implements both private key and public key algorithms and meets the power and performance specifications and is as small as 2.25 mm2 in 0.18- m 6LM CMOS.

The microcoded cryptography processor targets smart card applications and implements both private key and public key algorithms and meets the power and performance specifications and is as small as 2.25 mm/sup 2/ in 0.18-/spl mu/m 6LM CMOS.@article{Eslami2006AnAU, title={An area-efficient universal cryptography processor for smart cards}, author={Yadollah Eslami and Ali Sheikholeslami and P. Glenn Gulak and Shoichi Masui and Kenji Mukaida}, journal={IEEE Transactions on Very Large Scale Integration (VLSI) Systems}, year={2006}, volume={14}, pages={43-56} }

The microcoded cryptography processor targets smart card applications and implements both private key and public key algorithms and meets the power and performance specifications and is as small as 2.25 mm/sup 2/ in 0.18-/spl mu/m 6LM CMOS.

The micro coded cryptography processor is designed for smart card applications, supporting both private key and public key algorithms while meeting the required power and performance standards. Impressively, it is as small as 2.25 mm2 using 0.18-μm 6LM CMOS technology.The microcoded cryptography processor targets smart card applications and implements both private key and public key algorithms and meets the power and performance specifications and is as small as 2.25 mm/sup 2/ in 0.18-/spl mu/m 6LM CMOS.

eslami et al.: area-efficient universal cryptography processor for smart cards 45 throughput requirements of smart cards and occupies 2.25 mm in 0.18- m 6LM CMOS.

The microcoded cryptography processor targets smart card applications and implements both private key and public key algorithms and meets the power and performance specifications and is as small as 2.25 mm 2 in 0.18-µm 6LM CMOS. The microcoded cryptography processor targets smart card applications and implements both private key and public key algorithms and meets the power and performance specifications and is as.This paper proposes a high-performance ASIP (Application specific instruction set processor) for five standard cryptographic algorithms in-cluding both block ciphers (AES, Camellia, and ARIA) and stream ciphers (ZUC and SNOW 3G).

The microcoded cryptography processor targets smart card applications and implements both private key and public key algorithms and meets the power and performance specifications and is as small as 2.25 mm2 in 0.18- m 6LM CMOS.The microcoded cryptography processor targets smart card applications and implements both private key and public key algorithms and meets the power and performance specifications and is as small as 2.25 mm/sup 2/ in 0.18-/spl mu/m 6LM CMOS.

nfc tag reader programmers

@article{Eslami2006AnAU, title={An area-efficient universal cryptography processor for smart cards}, author={Yadollah Eslami and Ali Sheikholeslami and P. Glenn Gulak and Shoichi Masui and Kenji Mukaida}, journal={IEEE Transactions on Very Large Scale Integration (VLSI) Systems}, year={2006}, volume={14}, pages={43-56} }

An Area

nintendo 3ds nfc reader writer bundle

Open source tool developped and showed for Hackito Ergo Sum 2012 - "Hacking the NFC credit cards for fun and debit ;)" Reads NFC credit card personal data (gender, first .

universal cryptography processor for smart cards|An area